# Introduction To Microprocessor

#### 1.1 TERMS USED IN MICROPROCESSOR LITERATURE

Bit : A digit of the binary number or code is called a bit.

Nibble The 4-bit (4-digit) binary number or code is called a nibble.

**Byte** The 8-bit (8-digit) binary number or code is called a byte.

Word : The 16-bit (16-digit) binary number or code is called a word.

Double Word : The 32-bit (32-digit) binary number or code is called a double word.

Multiple Word : The 64, 128, ... bit/digit binary numbers or codes are called multiple words.

Data : The quantity (binary number/code) operated by an instruction of a program

is called data. The size of data is specified as bit, byte, word, etc.

Address : Address is an identification number (in binary) for memory locations.

The 8085 processor uses a 16-bit address for memory.

(or Addressability)

Memory Word Size: The memory word size or addressability is the size of binary information that can be stored in a memory location. The memory word size for an

8085 processor-based system is 8-bit.

[ Address and program codes in a microprocessor system are given in binary (i.e., as a combination of "0" and "1"). With n-bit binary we can generate 2<sup>n</sup> different binary codes or addresses.]

Microprocessor

: The microprocessor is a program-controlled semiconductor device (IC), which fetches instruction and data (from memory), decodes and executes instructions. It is used as CPU (Central Processing Unit) in computers. The basic functional blocks of a microprocessor are ALU (Arithmetic Logic Unit), an array of registers and a control unit. The microprocessor is identified with the size of data the ALU of the processor can work with at a time. The 8085 processor has a 8-bit ALU; hence, it is called a 8-bit processor. The 80486 processor has a 32-bit ALU; hence, it is called a 32-bit processor.

Bus

: A bus is a group of conducting lines that carries data, address and control signals. Buses can be classified into Data bus, Address bus and Control bus. The group of conducting lines that carries data is called a data bus.

The group of conducting lines that carries address is called an address bus.

The group of conducting lines that carries control signals is called a control bus.

**CPU** Bus

: The group of conducting lines that are directly connected to the microprocessor is called a CPU bus. In a CPU bus, the signals are multiplexed, i.e., more than one signal is passed through the same line but at different timings.

System Bus

: The group of conducting lines that carries data, address and control signals in a microcomputer system is called System bus. Multiplexing is not allowed in a system bus.

[In microprocessor-based systems, each bit of information (data/address/control signal) is sent through a separate conducting line. Due to practical limitations, the manufacturers of microprocessors may provide multiplexed pins, i.e., one pin is used for more than one purpose. This leads to a multiplexed CPU bus. For example, in an 8085 processor, the address and data are sent through the same pins but at different timings. But when the system is formed, the multiplexed bus lines should be demultiplexed by using latches, ports, transceivers, etc. The demultiplexed bus lines are called system bus. In a system bus, separate conducting lines will be provided for each bit of data, address and control signals.]

Clock

: A clock is a square wave used to synchronize various devices in the microprocessor and in the system. Every microprocessor system requires a clock for its functioning. The time taken for the microprocessor and the system to execute an instruction or program are measured only in terms of the time period of its clock.

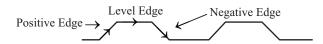

A clock has three edges: rising edge (positive edge), level edge and falling edge (negative edge). The device is made sensitive to any one of the edges for better functioning (it means that the device will recognize the clock only when the edge is asserted or arrived).

Tristate Logic

: Almost all the devices used in a microprocessor-based system use tristate logic. In devices with tristate logic, three logic levels will be available: **High** state, **Low** state and **High impedance** state.

The **high** and **low** level states are normal logic levels for data, address or control signals. The **high impedance** state is an electrical open-circuit condition. The **high impedance** state is provided to keep the device electrically isolated from the system. The tristate devices will normally remain in the **high impedance** state and their pins are physically connected in the system bus but electrically isolated. In the **high impedance** state, they cannot receive or send any signal or information. These devices are provided with chip enable/chip select pins. When the signal at this pin is asserted to the right level, they come out from the **high impedance** state to normal levels.

#### 1.2 EVOLUTION OF MICROPROCESSORS

History tells us that it was the ancient Babylonians who first began using the abacus (a primitive calculator made of beads) in about 500 BC. This simple calculating machine eventually sparked the human mind into the development of calculating machines that use gears and wheels (Blaise Pascal in 1642). The giant computing machines of the 1940s and 1950s were constructed with relays and vacuum tubes. Next, the transistor and solid-state electronics were used to build the mighty computers of the 1960s. Finally, the advent of the Integrated Circuit (IC) led to the development of the microprocessor and microprocessor-based computer systems.

In 1971, INTEL Corporation released the world's first microprocessor the INTEL 4004, a 4-bit microprocessor. It addresses 4096 memory locations of 4-bit word size. The instruction set consists of 45 different instructions. It is a monolithic IC employing large-scale integration in PMOS technology. The INTEL 4004 was soon followed by a variety of microprocessors, with most of the major semiconductor manufacturers producing one or more types.

# **First-Generation Microprocessors**

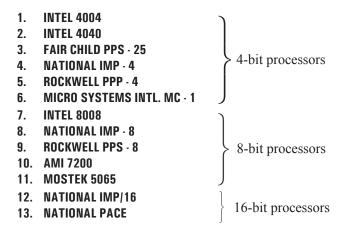

The microprocessors introduced between 1971 and 1973 were the first-generation processors. They were designed using PMOS technology. This technology provided low cost, slow speed and low output currents and was not compatible with TTL (Transistor Transistor Logic) levels.

The first-generation processors required a lot of additional support ICs to form a system, sometimes as high as 30 ICs. The 4-bit processors are provided with only 16 pins, but 8-bit and 16-bit processors are provided with 40 pins. Due to limitations of pins, the signals are multiplexed. A list of first-generation microprocessors are as follows:

#### **Second-Generation Microprocessors**

The second-generation microprocessors appeared in 1973 and were manufactured using the NMOS technology. The NMOS technology offers faster speed and higher density than PMOS and it is TTL compatible. Some of the second-generation processors are as follows:

### Characteristics of Second-Generation Microprocessors

- 1. Larger chip size (170 × 200 mil). [1mil =  $10^{-3}$  inch]

- 2. 40 pins.

- 3. More numbers of on-chip decoded timing signals.

- 4. The ability to address large memory spaces.

- 5. The ability to address more IO ports.

- 6. Faster operation.

- 7. More powerful instruction set.

- 8. A greater number of levels of subroutine nesting.

- 9. Better interrupt-handling capabilities.

# **Third-Generation Microprocessors**

After 1978, the third-generation microprocessors were introduced. These are 16-bit processors and designed using HMOS (High density MOS) technology. Some of the third generation microprocessor are given below:

3. INTEL 80186 6. MOTOROLA 68010 9. TEXAS INSTRUMENTS TMS 99000

The HMOS technology offers better Speed Power Product (SPP) and higher packing density than NMOS.

Speed Power Product (SPP) = Speed × Power

Unit of SPP = Nanoseconds × Milliwatts

= Picojoules

1. Speed Power Product of HMOS is four times better than NMOS.

SPP of NMOS = 4 picojoules (pJ) SPP of HMOS = 1 picojoules (pJ)

2. Circuit densities provided by HMOS are approximately twice those of NMOS.

Packing density of NMOS = 1852.5 gates/mm<sup>2</sup>

Packing density of HMOS = 4128 gates/mm<sup>2</sup> (1 mm = 10<sup>-6</sup> metre)

# Characteristics of Third-Generation Microprocessors

- Provided with 40/48/64 pins.

- High speed and very strong processing capability.

- Easier to program.

- Allow for dynamically relocatable programs.

- Size of internal registers are 8/16/32 bits.

- The processor has multiply/divide arithmetic hardware.

- Physical memory space is from 1 to 16 megabytes.

- The processor has segmented addresses and virtual memory features.

- More powerful interrupt-handling capabilities.

- Flexible IO port addressing.

- Different modes of operations (e.g., user and supervisor modes of M68000).

# Fourth-Generation Microprocessors

The fourth-generation microprocessors were introduced in the year 1980. These generation processors are 32-bit processors and are fabricated using the low-power version of the HMOS technology called HCMOS. These 32-bit microprocessors have increased sophistications that compete strongly with mainframes. Some of the fourth-generation microprocessors are given below:

1. INTEL 80386 4. MOTOROLA M68020 7. MOTOROLA MC88100

2. INTEL 80486 5. BELLMAC - 32

3. NATIONAL NS16032 6. MOTOROLA M68030

# Characteristics of Fourth-Generation Microprocessors

- 1. Physical memory space of  $2^{24}$  bytes = 16 MB (megabytes).

- 2. Virtual memory space of  $2^{40}$  bytes = 1TB (terabytes).

- 3. Floating-point hardware is incorporated.

- 4. Supports increased number of addressing modes.

### Fifth-Generation Microprocessors

In microprocessor technology, INTEL has taken a leading edge and is developing more and more new processors. The latest processor by INTEL is the **pentium** which is considered a fifth-generation processor. The pentium is a 32-bit processor with 64-bit data bus and is available in a wide range of clock speeds from 60 MHz to 3.2 GHz. With improvement in semiconductor technology, the processing speed of microprocessors has increased tremendously. The 8085 released in the year 1976 executes 0.5 **M**illion Instructions Per Second (0.5 MIPS). The 80486 executes 54 Million Instructions Per Second. The pentium is optimized to execute two instructions in one clock period. Therefore, a pentium processor working at 1 GHz clock can execute 2000 **M**illion Instructions Per Second (2000 MIPS). The various processors released by INTEL are listed in Appendix III.

# 1.3 FUNCTIONAL BUILDING BLOCKS OF A MICROPROCESSOR

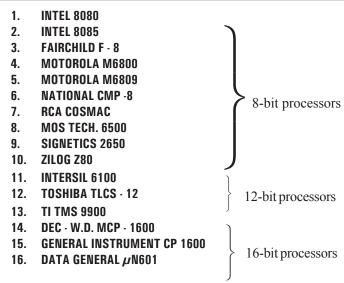

A microprocessor is a programmable IC which is capable of performing arithmetic and logical operations. The basic functional block diagram of a microprocessor is shown in Fig. 1.1.

The basic functional blocks of a microprocessor are ALU, Flag register, Register array, Program Counter (PC)/Instruction Pointer (IP), Instruction decoding unit, and the Timing and Control unit.

Fig. 1.1: Block diagram showing functional blocks of a microprocessor.

ALU is the computational unit of the microprocessor which performs arithmetic and logical operations on binary data. The various conditions of the result are stored as status bits called flags in the flag register. For example, consider sign flag. One of the bit positions of the flag register is called sign flag and it is used to store the status of sign of the result of the ALU operation (output data of ALU). If the result is negative then "1" is stored in the sign flag and if the result is positive then "0" is stored in the sign flag.

The register array is the internal storage device and so it is also called internal memory. The input data for ALU, the output data of ALU (result of computations) and any other binary information needed for processing are stored in the register array.

For any microprocessor, there will be a set of instructions given by its manufacturer. For doing any useful work with the microprocessor, we have to first write a program using these instructions, and store them in a memory device external to the microprocessor.

The instruction pointer generates the address of the instructions to be fetched from the memory and sends it through the address bus to the memory. The memory will send the instruction codes and data through the data bus. The instruction codes are decoded by the decoding unit and it sends information to the timing and control unit. The data is stored in the register array for processing by the ALU.

The control unit will generate the necessary control signals for internal and external operations of the microprocessor.

# 1.4 MICROPROCESSOR-BASED SYSTEM

# (ORGANIZATION OF A MICROCOMPUTER)

A microprocessor is a semiconductor device (or integrated circuit) manufactured by using the VLSI (Very Large Scale Integration) technique. It includes the ALU, the register arrays and the control circuit on a single chip. To perform a function or useful task we have to form a system by using the microprocessor as a CPU (Central Processing Unit) and interfacing the memory, input and output devices to it. A system designed by using a microprocessor as its CPU is called a microcomputer or a single board microcomputer. A microprocessor-based system consists of a microprocessor as the CPU, semiconductor memories like EPROM and RAM, an input device, an output device and interfacing devices. The memories, input devices, output devices and interfacing devices are called peripherals.

The commonly used EPROM and static RAM in microcomputers are given below:

| <b>EPROM</b>      | Static RAM          |

|-------------------|---------------------|

| INTEL 2708 (1 kB) | MOTOROLA 6208 (1kB) |

| INTEL 2716 (2 kB) | MOTOROLA 6216 (2kB) |

| INTEL 2732 (4kB)  | MOTOROLA 6232 (4kB) |

| INTEL 2764 (8kB)  | MOTOROLA 6264 (8kB) |

|                   |                     |

*Note:* kB refers to kilo bytes.

Popular input devices are keyboard, floppy disk, etc., and output devices are printer, LED and LCD displays, CRT monitor, etc.

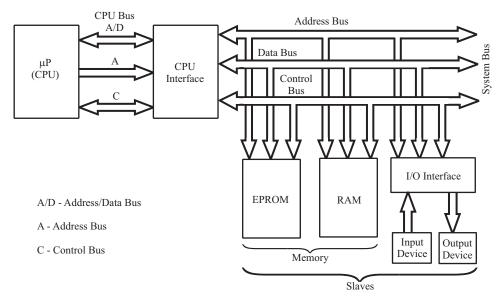

The block diagram of a microprocessor-based system (or organization of microcomputer) is shown in Fig. 1.2. In this system the microprocessor is the master and all other peripherals are slaves. The master controls all the peripherals and initiates all operations.

Fig. 1.2: Microprocessor-based system (organization of microcomputer).

Buses are groups of lines that carry data, addresses or control signals. The CPU bus has multiplexed lines, i.e., the same line is used to carry different signals. The CPU interface is provided to demultiplex the multiplexed lines to generate chip select signals and additional control signals. The system bus has separate lines for each signal.

All the slaves in the system are connected to the same system bus. But communication takes place between the master and one of the slaves at any one time. All the slaves have tristate logic and hence normally remain in **high impedance** state. The processor selects a slave by sending an address. When a slave is selected, it comes to the normal logic and communicates with the processor.

The EPROM memory is used to store permanent programs and data. The RAM memory is used to store temporary programs and data. The input device is used to enter the program, data and to operate the system. The output device is used for examining the results. Since the speed of IO devices does not match with the speed of the microprocessor, an interface device is provided between the system bus and the IO devices. Generally IO devices are slow devices.

The work done by the processor can be classified into the following three groups:

- 1. Work done internal to the processor.

- 2. Work done external to the processor.

- 3. Operations initiated by the slaves or peripherals.

The work done internal to the processor are additions, subtractions, logical operations, data transfer within registers, etc. The work done external to the processor are reading/writing the memory and reading/writing the IO devices or the peripherals. If the peripheral requires the attention of the master, then it can interrupt the master and initiate an operation.

The microprocessor is the master which controls all the activities of the system. To perform a specific job or task, the microprocessor has to execute a program stored in the memory. The program consists of a set of instructions stored in consecutive memory locations. In order to execute the program, the microprocessor issues address and control signals to fetch the instructions and data from the memory one by one. After fetching each instruction it decodes the instructions and performs the task specified by the instruction.

### 1.4.1 Concept of Multiplexing in a Microprocessor

Multiplexing is transferring different information at different well-defined times through the same lines. A group of such lines is called a multiplexed bus. The result of multiplexing is that fewer pins are required for microprocessors to communicate with the outside world.

Due to the pin number limitations, most microprocessors cannot provide simultaneously similar lines (such as address, data, status signals, etc.). Hence multiplexing of one or more of these buses is performed. Most often data lines are multiplexed with some or all address lines to form an address/data bus. (e.g., In 8085 the lower 8-address lines are multiplexed with data lines.) The status signals emitted by the microprocessor are sometimes multiplexed either with the data lines (as done in the INTEL 8080A) or with some of the address lines (as done in the INTEL 8086).

Whenever multiplexing is used, the CPU interface of the system must include the necessary hardware to demultiplex those lines to produce separate address, data and control buses required for the system. Demultiplexing of a multiplexed bus can be handled either at the CPU interface or locally at appropriate points in the system. Besides a slower system operation, a multiplexed bus also results in additional interface hardware requirements.

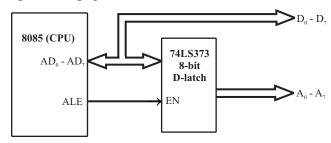

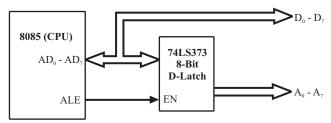

# 1.4.2 Demultiplexing of Address/Data Lines in 8085 Microprocessor

In order to demultiplex the address/data lines (of the processor), the processor provides a signal called the ALE (Address Latch Enable). The ALE is asserted **high** and then **low** by the processor at the beginning of every machine cycle. At the same time the low byte address is given out through the  $AD_0$  -  $AD_7$  lines. The demultiplexing of address/data lines using an 8-bit D-latch 74LS373 is shown in Fig. 1.3.

The ALE is connected to the enable pin (EN) of an external 8-bit latch. When the ALE is asserted **high** and then **low**, the addresses are latched into the output lines of the latch. It holds the low byte of the address until the next machine cycle. After latching the address, the  $AD_0$  -  $AD_7$  lines are free for data transfer. The first T-state of every machine cycle is used for address latching in 8085 and the remaining T-states are used for reading or writing operation.

Fig. 1.3: Demultiplexing of address and data lines in an 8085 processor.

### 1.5 INTEL 8085 PINS, SIGNALS AND ARCHITECTURE

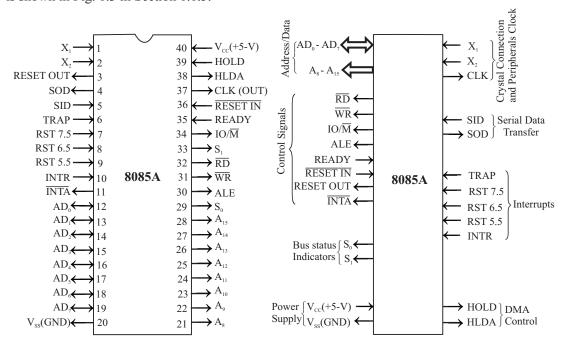

The INTEL 8085 is an 8-bit microprocessor released in the year 1976. The 8085 was originally designed using NMOS technology but now it is manufactured using HMOS technology and contains approximately 6500 transistors. The 8085 is packed in a 40-pin DIP (**D**ual In-line **P**ackage) and requires a single 5V supply.

The 8085 has an internal clock oscillator. It generates a clock signal internally and divides by two for use as internal clock. This internal clock is also given out through the CLK pin for the clock requirement of peripheral devices.

The NMOS 8085 is available in two versions: 8085A and 8085A-2, with a maximum internal clock frequency of 3.03 MHz and 5 MHz respectively. The enhanced version of the 8085 is designed with HMOS transistors. It is available in three versions: 8085AH, 8085AH-2 and 8085AH-1 with maximum internal clock of 3 MHz, 5 MHz and 6 MHz respectively.

The basic data size of an 8085 is 8-bit. Therefore the memory word size of the memories interfaced with a 8085 processor is also 8-bit or byte. The 8085 uses a 16-bit address to access memory and hence it can address up to  $2^{16} = 65,536_{10} = 64 \,\mathrm{k}$  memory locations. Since, one byte of information can be stored in one memory location, the maximum memory capacity of an 8085-based system is 64 kilobytes. For accessing IO-mapped devices, the 8085 uses a separate 8-bit address and so it can generate  $2^8 = 256_{10}$  IO addresses.

# 1.5.1 Pin Configuration of 8085 Microprocessor

The pin configuration of an 8085 microprocessor is shown in Fig. 1.4. The signals of the 8085 are listed in Table 1.1. The 8085 has 8 pins  $AD_0$  to  $AD_7$  for data transfer, which are multiplexed with low byte of address. The 8085 provides a signal ALE (Address Latch Enable) to demultiplex the low byte address and data using an external latch. The demultiplexing of address and data lines in an 8085 is shown in Fig. 1.3 in Section 1.1.5.

Fig. 1.4: 8085 microprocessor signals and pin assignment.

During memory access, the 16-bit memory address are output on  $AD_0$  to  $AD_7$  and  $A_8$  to  $A_{15}$  lines. During IO access of IO-mapped devices the 8-bit IO address are output on both  $AD_0$  to  $AD_7$  and  $A_8$  to  $A_{15}$  lines. The 8085 processor differentiates the memory and IO address using the signal  $IO/\overline{M}$ . When the processor outputs a memory address, the  $IO/\overline{M}$  is asserted **low** and when the processor outputs an IO address, the  $IO/\overline{M}$  is asserted **high**.

The  $\overline{RD}$  signal is asserted **low** by the processor during a memory or IO read operation. The  $\overline{WR}$  signal is asserted **low** by the processor during a memory or IO write operation. The  $S_0$  and  $S_1$  are bus status indicators. The output signals on these lines during various bus activity (or machine cycles) are listed in Table 1.2.

Table 1.1: 8085 Signal Description Summary

| Pin Name                          | Description                               | Type             |

|-----------------------------------|-------------------------------------------|------------------|

| AD <sub>0</sub> - AD <sub>7</sub> | Address/Data Bidirectional, Trista        |                  |

| A <sub>8</sub> - A <sub>15</sub>  | Address                                   | Output, Tristate |

| ALF                               | Address latch enable                      | Output, Tristate |

| RD                                | Read control                              | Output, Tristate |

| WR                                | Write control                             | Output, Tristate |

| $IO/\overline{M}$                 | IO or memory indicator                    | Output, Tristate |

| S <sub>0</sub> , S <sub>1</sub>   | Bus state indicators                      | Output           |

| READY                             | Wait state request                        | Input            |

| SID                               | Serial input data                         | Input            |

| SOD                               | Serial output data                        | Output           |

| HOLD                              | Hold request Input                        |                  |

| HLDA                              | Hold acknowledge Output                   |                  |

| INTR                              | Interrupt request Input                   |                  |

| TRAP                              | Nonmaskable interrupt request             | Input            |

| RST 5.5                           | Hardware vectored interrupt request Input |                  |

| RST 6.5                           | Hardware vectored interrupt request Input |                  |

| RST 7.5                           | Hardware vectored interrupt request Input |                  |

| INTA                              | Interrupt acknowledge                     | Output           |

| RESET IN                          | System reset Input                        |                  |

| RESET OUT                         | Peripherals reset Output                  |                  |

| X <sub>1</sub> , X <sub>2</sub>   | Crystal or RC connection Input            |                  |

| CLK (OUT)                         | Clock signal                              | Output           |

| V <sub>cc</sub>                   | +5 V                                      | Power supply     |

| V <sub>ss</sub>                   | Ground                                    | Power supply     |

**Note:** A overbar on the signal, indicates that it is active low. (i.e., the signal is normally high and when the signal is activated it is low).

**Table 1.2: Bus Status Signals**

| $IO/\overline{M}$ | S <sub>1</sub> | S <sub>0</sub> | Operation performed by the 8085 |

|-------------------|----------------|----------------|---------------------------------|

| 0                 | 0              | 1              | Memory write                    |

| 0                 | 1              | 0              | Memory read                     |

| 1                 | 0              | 1              | IO write                        |

| 1                 | 1              | 0              | IO read                         |

| 0                 | 1              | 1              | Opcode fetch                    |

| 1                 | 1              | 1              | Interrupt acknowledge           |

READY is an input signal that can be used by slow peripherals to get extra time in order to communicate with the 8085. The 8085 will work only when READY is tied to logic **high**. Whenever READY is tied to logic **low**, the 8085 will enter a wait state. When the system has slow peripheral devices, additional hardware is provided in the system to make the READY input **low** during the required extra time while executing a machine cycle, so that the processor will remain in wait state during this extra time.

The HOLD and HLDA signals are used for **D**irect **M**emory **A**ccess (DMA) type of data transfer. This type of data transfers are achieved by employing a DMA controller in the system. When DMA is required, the DMA controller will place a **high** signal on the HOLD pin of the 8085. When the HOLD input is asserted **high**, the processor will enter a wait state and drive all its tristate pins to a **high impedance** state and send an acknowledgement signal to the DMA controller through the HLDA pin. Upon receiving the acknowledgement signal, the DMA controller will take control of the bus and perform DMA transfer and at the end it asserts HOLD signal **low**. When HOLD is asserted **low** the processor will resume its execution.

The 8085 has five interrupt pins. The order of priority of the interrupts is TRAP, RST 7.5, RST 6.5, RST 5.5 and INTR. The interrupts TRAP, RST 7.5, RST 6.5 and RST 5.5 are hardware vectored interrupts and are enabled by appropriate signals at the appropriate pins of the 8085. When a vectored interrupt is enabled and if it is accepted then the program execution branches to the vector addresses specified by INTEL. The interrupts RST 7.5, RST 6.5 and RST 5.5 are maskable interrupts by software.

The INTR is enabled by appropriate signals at its pin. In order to service the INTR, one of the eight opcodes (RST 0 to RST 7) has to be provided on the  $AD_0$  -  $AD_7$  bus by external logic. The 8085 then executes this instruction and vectors to the appropriate address to service the interrupt. The vector address for an interrupt RST n is given by  $(08 \times n)_H$ . The vector addresses of the interrupts of 8085 are listed in Table 1.3. (The interrupt TRAP is RST 4.5.)

Table 1.3: Vector Addresses of Interrupts

| Interrupt | Vector address    |

|-----------|-------------------|

| RST 0     | 0000 <sub>H</sub> |

| RST 1     | 0008 <sub>H</sub> |

| RST 2     | 0010 <sub>H</sub> |

| RST 3     | 0018 <sub>H</sub> |

| RST 4     | 0020 <sub>H</sub> |

| TRAP      | 0024 <sub>H</sub> |

| Interrupt | Vector address    |

|-----------|-------------------|

| RST 5     | 0028 <sub>H</sub> |

| RST 5.5   | 002C <sub>H</sub> |

| RST 6     | 0030 <sub>H</sub> |

| RST 6.5   | 0034 <sub>H</sub> |

| RST 7     | 0038 <sub>H</sub> |

| RST 7.5   | 003C <sub>H</sub> |

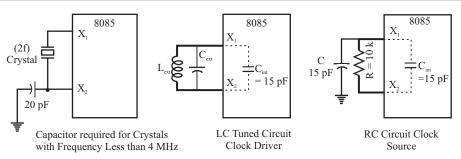

The 8085 has the clock generation circuit on the chip but an external quartz crystal or LC circuit or RC circuit should be connected at the pins  $X_1$  and  $X_2$ . The frequency at  $X_1$  and  $X_2$  is divided by two internally and used as an internal clock. The frequency of the output clock signal at the CLK (OUT) pin is same as that of the internal clock.

$\overline{RESET\ IN}$  is the system reset input signal and it is used to bring the processor to a known state. For proper reset, the  $\overline{RESET\ IN}$  pin should be held **low** for at least three clock periods. When pin is asserted **low**, the program counter, instruction register, interrupt mask bits and all internal registers are cleared/reset. Also the RESET OUT signal is asserted **high** to clear/reset all the peripheral devices in the system. After a reset, the content of the program counter will be  $0000_H$  and so the processor will start executing the program stored at  $0000_H$ .

The pins SID and SOD can be used for serial data communication between the 8085 and any serial device under software control.

# 1.5.2 Driving X, and X, Inputs in 8085 Microprocessor

The  $X_1$  and  $X_2$  pins of an 8085 processor are provided to connect an external quartz crystal or LC circuit. It can also be driven by an RC circuit or an external clock source. This connection is necessary for the internal oscillator to generate the clock signal for the processor. An oscillator consists of an amplifier and a feedback circuit. The feedback circuit of an oscillator can be of RC type, LC type or quartz crystal (a quartz crystal is electrically equivalent to an RLC circuit.) Also the feedback circuit decides the frequency of the signal generated by the oscillator.

In an 8085 processor, the oscillator circuit is provided internally except the feedback circuit. This feature facilitates the system designer to choose his own frequency for clock signals. But this frequency should not exceed the maximum clock frequency specified by the manufacturer. Another reason for keeping feedback circuit external to the processor is that the high Q circuits (quartz crystal or large values of L) cannot be fabricated by IC technology.

In an 8085, the frequency generated by the oscillator circuit will be double that of the internal clock frequency. (The maximum clock frequencies specified by the manufacturer are internal clock frequencies.) In other words, the frequency at  $X_1 - X_2$  pins of an 8085 is divided by two internally. This means that in order to obtain an internal clock of 3.03 MHz, a clock source of 6.06 MHz must be connected to  $X_1 - X_2$ . (Crystal/LC/RC should be designed for double the internal frequency.)

Quartz crystals are the best choice for connecting at  $X_1$  -  $X_2$ , because they are less expensive, highly stable, have a large Q, occupy a very small space and frequencies do not drift with ageing. For crystals with less than 4 MHz, a capacitor of 20 pF should be connected between  $X_2$  and ground to ensure the starting up of the crystal at the right frequency.

When an LC circuit is used, the value of  $L_{ext}$  and  $C_{ext}$  can be chosen using the formula,

$$f = \frac{1}{2\pi L_{ext}(C_{ext} + C_{int})}$$

Fig. 1.5: Clock driver circuits for an 8085.

To minimize the variations in frequency, it is recommended that the value for  $C_{\rm ext}$  should be chosen which is twice that of  $C_{\rm int}$  or 30 pF. The use of LC circuit is not recommended for external frequencies higher than 5 MHz.

An RC circuit may also be used as the clock source for the 8085A if an accurate clock frequency is of no concern. Its advantage is the low component cost. The values shown in Fig. 1.5 are for generating an approximate external frequency of 3 MHz. Note that frequencies higher or lower than 3 MHz should not be attempted on this circuit.

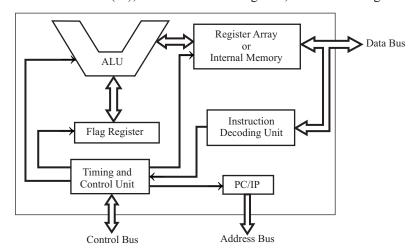

# 1.5.3 Hardware Architecture of 8085 Microprocessor

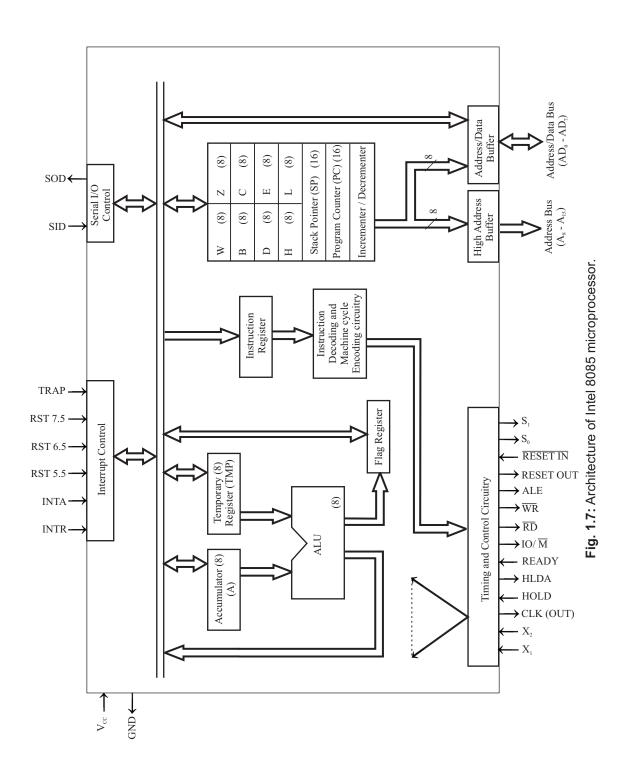

The architecture of an 8085 is shown in Fig. 1.7. The 8085 includes an ALU, a timing and control unit, a instruction register and a decoder, a register array, an interrupt control and a serial IO control.

The ALU performs the arithmetic and logical operations. The operations performed by the ALU of an 8085 are addition, subtraction, increment, decrement, logical AND, OR, EXCLUSIVE-OR, compare, complement and left/right shift. The accumulator and temporary register are used to hold the data during an arithmetic/logical operation. After an operation the result is stored in the accumulator and the flags are set or reset according to the result of the operation. The accumulator and flag register together is called the **P**rogram **S**tatus **W**ord (PSW).

There are five flags in an 8085: Sign Flag (SF), Zero Flag (ZF), Auxiliary Carry Flag (AF), Parity Flag (PF) and Carry Flag (CF). The bit positions reserved for these flags in the flag register are shown in Fig. 1.6.

| $D_7$ | $D_6$ | $D_5$ | $D_4$ | $D_3$ | $D_{2}$ | $\mathbf{D}_{\scriptscriptstyle 1}$ | $D_{\scriptscriptstyle 0}$ |

|-------|-------|-------|-------|-------|---------|-------------------------------------|----------------------------|

| SF    | ZF    |       | AF    |       | PF      |                                     | CF                         |

**Fig. 1.6:** Bit positions of various flags in the flag register of 8085.

After an ALU operation if the most significant bit of the result is 1, the sign flag is set. The zero flag is set if the ALU operation results in zero and it is reset if the result is nonzero. In an arithmetic operation, when a carry is generated by the lower nibble, the auxiliary carry flag is set. After an arithmetic or logical operation if the result has an even number of 1's, the parity flag is set, otherwise it is reset.

If an arithmetic operation results in a carry, the carry flag is set, otherwise it is reset. Among the five flags, the AF flag is used internally for BCD arithmetic and other four flags can be used by the programmer to check the conditions of the result of an operation.

The **timing and control unit** synchronizes all the microprocessor operations with the clock, and generates the control signals necessary for communication between the microprocessor and the peripherals.

When an instruction is fetched from the memory it is placed in the instruction register. Then it is decoded and encoded into various machine cycles. Apart from the **Accumulator** (A-register) there are six general purpose programmable registers B, C, D, E, H and L. They can be used as 8-bit registers or paired to store 16-bit data. The allowed pairs are BC, DE and HL. The temporary registers TMP, W and Z cannot be used by the programmer.

The Stack Pointer SP holds the address of the stack top. The stack is a sequence of RAM memory locations defined by the programmer. The stack is used to save the content of the registers during the execution of a program.

The Program Counter (PC) keeps track of program execution. To execute a program the starting address of the program is loaded in the program counter. The PC sends out an address to fetch a byte of instruction from memory and increment its content automatically. Hence when a byte of instruction is fetched, the PC holds the address of the next byte of the instruction or the next instruction.

# 1.5.4 Instruction Execution and Data Flow in 8085 Microprocessor

The program instructions are stored in the memory, which is an external device. In order to execute a program in an 8085, the starting address of the program should be loaded in the program counter. The 8085 outputs the contents of the program counter to the address bus and asserts the read control signal **low**. Also, the program counter is incremented.

The address and the read control signal enables the memory to output the content of the memory location on the data bus. Now the content of the data bus is the opcode of an instruction. The read control signal is made **high** by the timing and control unit after a specified time. At the rising edge of read control signals, the opcode is latched into the microprocessor internal bus and placed in the instruction register.

The instruction decoding unit decodes the instructions and provides information to the timing and control unit to take further action.

#### 1.6 INTEL 8086 MICROPROCESSOR

The INTEL 8086 is the first 16-bit processor released by INTEL in the year 1978. The 8086 is designed using the HMOS technology and now it is manufactured using HMOS III technology and contains approximately 29,000 transistors. The 8086 is packed in a 40-pin DIP and requires a single 5-V supply.

The 8086 does not have an internal clock circuit. The 8086 requires an external asymmetric clock source with 33% duty cycle. An 8284 clock generator is used to generate the required clock for 8086. The maximum internal clock of 8086 is 5 MHz. The other versions of 8086 with different clock rates are 8086-1, 8086-2 and 8086-4 with maximum internal clock frequency of 10 MHz,

8 MHz and 4 MHz respectively.

The 8086 uses a 20-bit address to access memory and hence it can directly address up to one megabytes (220 = 1 Mega) of memory space. The one megabyte (1MB) of addressable memory space of 8086 are organized as two memory banks of 512 kilobytes each (512 kB + 512 kB = 1MB).

The memory banks are called even (or lower) bank and odd (or upper) bank. The address line  $A_0$  is used to select even bank and the control signal  $\overline{BHE}$  is used to select odd bank.

For accessing IO-mapped devices, the 8086 uses a separate 16-bit address, and so the 8086 can generate  $64k(2^{16})$  IO addresses. The signal M/ $\overline{\text{IO}}$  is used to differentiate the memory and IO addresses. For memory address the signal M/ $\overline{\text{IO}}$  is asserted **high** and for IO address the signal M/IO is asserted **low** by the processor.

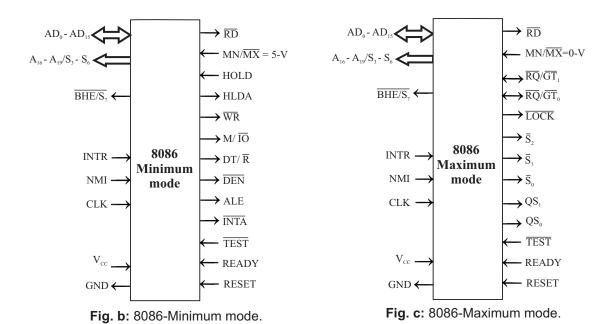

The 8086 can operate in two modes: minimum mode and maximum mode. The mode is decided by a signal at  $MN/\overline{MX}$  pin. When the  $MN/\overline{MX}$  is tied **high** it works in minimum mode and the system is called a uniprocessor system. When  $MN/\overline{MX}$  is tied **low** it works in maximum mode and the system is called a multiprocessor system. Usually the pin  $MN/\overline{MX}$  is permanently tied to **low** or **high** so that the 8086 system can work in any one of the two modes. The 8086 can work with an 8087 coprocessor in maximum mode. In this mode an external bus controller 8288 is required to generate bus control signals.

The 8086 has two families of processors. They are 8086 and 8088. The 8088 uses 8-bit data bus externally but 8086 uses 16-bit data bus externally. The 8086 access memory is in words but 8088 access memory is in bytes. IBM designed its first **P**ersonal Computer (PC) using an INTEL 8088 microprocessor as the CPU.

#### 1.6.1 Pins and Signals of INTEL 8086

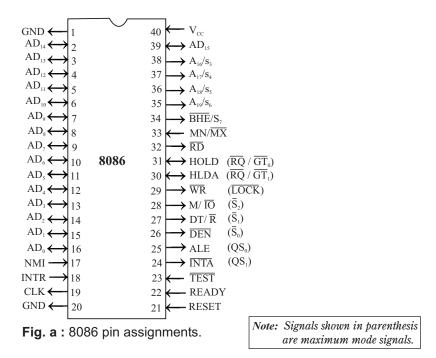

The 8086 pins and signals are shown in Fig. 1.13. The 8086 is a 40-pin IC and all the 8086 pins are TTL compatible. The signal assigned to pins 24 to 31 is different for minimum and maximum mode of operation. The signal assigned to all the other pins are common for minimum and maximum mode of operation.

Fig. 1.8: 8086 signals and pin assignment.

**TABLE 1.4: Common Signals**

| Name                                                             | Description/Function           | Туре                    |

|------------------------------------------------------------------|--------------------------------|-------------------------|

| AD <sub>15</sub> - AD <sub>0</sub>                               | Address/Data                   | Bidirectional, Tristate |

| A <sub>19</sub> /S <sub>6</sub> -A <sub>16</sub> /S <sub>3</sub> | Address/Status                 | Output, Tristate        |

| BHE/S <sub>7</sub>                                               | Bus high enable/Status         | Output, Tristate        |

| MN/MX                                                            | Minimum/Maximum mode control   | Input                   |

| RD                                                               | Read control                   | Output, Tristate        |

| TEST                                                             | Wait on test control Input     |                         |

| READY                                                            | Wait state control Input       |                         |

| RESET                                                            | System reset Input             |                         |

| NMI                                                              | Non-maskable interrupt request | Input                   |

| INTR                                                             | Interrupt request Input        |                         |

| CLK                                                              | System clock Input             |                         |

| V <sub>cc</sub>                                                  | + 5-V                          | Power supply input      |

| GND                                                              | Ground                         | Power supply ground     |

TABLE 1.5: Minimum Mode Signals [MN /  $\overline{\text{MX}}$  =  $V_{cc}$  (Logic high)]

| Name | Description / Function           | Type             |

|------|----------------------------------|------------------|

| HOLD | Hold request                     | Input            |

| HLDA | Hold acknowledge                 | Output           |

| WR   | Write control                    | Output, Tristate |

| M/IO | Memory/IO control Output, Trista |                  |

| DT/R | Data transmit/Receive            | Output, Tristate |

| DEN  | Data enable Output, Tristate     |                  |

| ALE  | Address latch enable             | Output           |

| ĪNTĀ | Interrupt acknowledge            | Output           |

TABLE 1.6: Maximum Mode Signals [MN /  $\overline{\text{MX}}$  = GROUND (Logic low)]

| Name                                                              | Description/Function             | Туре             |

|-------------------------------------------------------------------|----------------------------------|------------------|

| $\overline{RQ}/\overline{GT}_1$ , $\overline{RQ}/\overline{GT}_0$ | Request/Grant bus access control | Bidirectional    |

| LOCK                                                              | Bus priority lock control        | Output, Tristate |

| $\overline{S}_2$ , $\overline{S}_1$ , $\overline{S}_0$            | Bus cycle status                 | Output, Tristate |

| QS <sub>1</sub> , QS <sub>0</sub>                                 | Instruction queue status         | Output           |

|                                                                   |                                  |                  |

# 1.6.2 Common Signals

The signals common for minimum and maximum mode are listed in Table-1.4. The lower sixteen lines of address are multiplexed with data and the upper four lines of address are multiplexed with status signals. During the first clock period of a bus cycle the entire 20-bit address is available on these lines. During all other clock periods of a bus cycle, the data and status signals will be available on these lines.

The status signals on  $S_3$  and  $S_4$  specifies the segment register used for calculating the physical address. The output on the status lines  $S_3$  and  $S_4$  when the processor is accessing various segments are listed in Table 1.7.

| Status signal |       | Segment register   |

|---------------|-------|--------------------|

| $S_4$         | $S_3$ |                    |

| 0             | 0     | Extra segment      |

| 0             | 1     | Stack segment      |

| 1             | 0     | Code or no segment |

| 1             | 1     | Data segment       |

**Table 1.7: Status Signals During Memory Segment Access**

The status lines  $S_3$  and  $S_4$  can be used to expand the memory up to 4 Mb. The status line  $S_5$  indicates the status of an 8086 interrupt enable flag. A **low** on the line  $S_6$  indicates that 8086 is on the bus (i.e., it indicates that 8086 is the bus master) and during hold acknowledge this pin is driven to **high impedance** state. The output signal  $\overline{BHE}$  on the first T-state of a bus cycle is maintained as status signal  $S_7$  on the same pin.

The 8086 outputs a **low** on  $\overline{BHE}$  pin during read, write and interrupt acknowledge cycles when the data is to be transferred to the high-order data bus. The  $\overline{BHE}$  can be used in conjunction with  $AD_0$  to select memory banks.

When the processor reads from memory or an IO location it asserts  $\overline{\text{RD}}$  low. The  $\overline{\text{TEST}}$  input is tested by the WAIT instruction. The 8086 will enter a wait state after execution of the WAIT instruction, and it will resume execution only when  $\overline{\text{TEST}}$  is made low by an external hardware. This is used to synchronize an external activity to the processor internal operation.  $\overline{\text{TEST}}$  input is synchronized internally during each clock cycle on the leading edge of the clock signal.

INTR is the maskable interrupt and INTR must be held **high** until it is recognized to generate an interrupt signal. NMI is the non-maskable interrupt input activated by a leading edge signal.

RESET is the system reset input signal. For power-ON reset it is held **high** for 50 micro-second. For reset while working, it is held **high** for at least four clock cycles. When the processor is resetted, the DS, SS, ES, IP and flag register are cleared, Code Segment (CS) register is initialized to FFFF $_{\rm H}$  and queue is emptied. After reset the processor will start fetching instruction from 20-bit physical address FFFFO $_{\rm H}$ .

READY is an input signal to the processor, used by the memory or IO devices to get extra time for data transfer or to introduce **wait states** in the bus cycles. Normally READY is tied **high**. If the READY is tied **low**, the 8086 introduces wait states after second T-state of a bus cycle and it will complete the bus cycle only when READY is made **high** again.

CLK input is the clock signal that provides basic timing for the 8086 and bus controller. The 8086 does not have an on-chip clock generation circuit. Hence the 8284 clock generator chip is used to generate the required clock. A quartz crystal whose frequency is thrice that of the internal clock of 8086 must be connected to the 8284. The 8284 generates the clock at crystal frequency. It divides the generated clock by three and modifies the duty cycle to 33% and output on the CLK pin of the 8284. This CLK output of the 8284 must be connected to the 8086 CLK pin. The 8284 also provides the RESET and READY signal to an 8086.

# 1.6.3 Minimum Mode Signals

The minimum mode signals of an 8086 are listed in Table 1.5. For minimum mode of operation the  $MN/\overline{MX}$  pin is tied to  $V_{cc}(logic\ \textbf{high})$ . In minimum mode, the 8086 itself generates all bus control signals. The minimum mode signals are explained below:

- $DT/\overline{R}$  [Data Transmit/Receive] It is an output signal from the processor to control the direction of data flow through the data transceivers.

- **DEN** (*Data Enable*) It is an output signal from the processor used as output enable for the data transceivers.

- **ALE** (*Address Latch Enable*) It is used to demultiplex the address and data lines using external latches.

- M/IO It is used to differentiate memory access and IO access. For IN and OUT instructions it is asserted **low**. For memory reference instructions it is asserted **high.**

- WR It is a write control signal and it is asserted **low** whenever the processor writes data to memory or IO port.

- **INTA** (*Interrupt Acknowledge*) The 8086 output is asserted **low** on this line to acknowledge when the interrupt request is accepted by the processor.

- **HOLD** It is an input signal to the processor from other bus masters as a request to grant control of the bus. It is usually used by the DMA controller to get control of the bus.

- HLDA (Hold Acknowledge) It is an acknowledge signal by the processor to the master requesting the control of the bus through HOLD. The acknowledge is asserted high when the processor accepts the HOLD. [On accepting the hold the processor drives all the tristate pins to high impedance state and sends an acknowledgement to the device which requested HOLD. On receiving the acknowledgement the other master will take control of the bus.]

# 1.6.4 Maximum Mode Signals

The maximum mode signals of an 8086 are listed in Table 1.6. An 8086-based system can be made to work in maximum mode by grounding the  $MN/\overline{MX}$  pin (i.e.,  $MN/\overline{MX}$  is tied to logic **low**). In maximum mode, the pins 24 to 31 are redefined as follows:

$\overline{S_0}$ ,  $\overline{S_1}$ ,  $\overline{S_2}$  - These are status signals and they are used by the 8288 bus controller to generate bus timing and control signals. The status signals are decoded as shown in Table 1.8.

| Sta            | tus Sign       | al             | Machine Cycle         |

|----------------|----------------|----------------|-----------------------|

| S <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub> | Machine Cycle         |

| 0              | 0              | 0              | Interrupt acknowledge |

| 0              | 0              | 1              | Read IO port          |

| 0              | 1              | 0              | Write IO port         |

| 0              | 1              | 1              | Halt                  |

| 1              | 0              | 0              | Code access           |

| 1              | 0              | 1              | Read memory           |

| 1              | 1              | 0              | Write memory          |

| 1              | 1              | 1              | Passive/Inactive      |

**Table 1.8: Status Signals During Various Machine Cycles**

$\overline{RQ}/\overline{GT}_0$ , - (Bus Request/Bus Grant) These requests are used by the other local bus masters to force the processor to release the local bus at the end of the processor's current bus cycle These pins are bidirectional. The request on  $GT_0$  will have higher priority than  $GT_1$ .

# The bus request to an 8086 works as follows:

- 1. When a local bus master requires an system bus control, it sends a low pulse to the 8086.

- At the end of the current bus cycle, the processor (8086) drives its pins to high impedance state and sends an acknowledgement as a low pulse on the same pin to the device which had requested the bus control.

- 3. On receiving the acknowledgement the local master will take control of the system bus. After completing its work, at the end, the local bus master sends a low signal on the same pin to 8086 to inform the end of control. Now 8086 regains the control of the bus.

- **LOCK** It an output signal activated by the LOCK prefix instruction and remains active until the completion of the instruction prefixed by LOCK. The 8086 asserts the **LOCK** pin low while executing an instruction prefixed by LOCK to prevent other bus masters from gaining control of the system bus.

- QS<sub>1</sub>, QS<sub>0</sub> (Queue Status) The processor provides the status of queue on these lines. The queue status can be used by the external device to track the internal status of the queue in an 8086. The QS<sub>0</sub> and QS<sub>1</sub> are valid during the clock period following any queue operation. The output on QS<sub>0</sub> and QS<sub>1</sub> can be interpretted as shown in Table 1.9.

### **TABLE 1.9: QUEUE STATUS**

| Queu            | e status | 0                                      |  |

|-----------------|----------|----------------------------------------|--|

| QS <sub>1</sub> | $QS_0$   | Queue operation                        |  |

| 0               | 0        | No operation                           |  |

| 0               | 1        | First byte of an opcode from the queue |  |

| 1               | 0        | Empty the queue                        |  |

| 1               | 1        | Subsequent byte from the queue         |  |

#### 1.6.5 Architecture of INTEL 8086

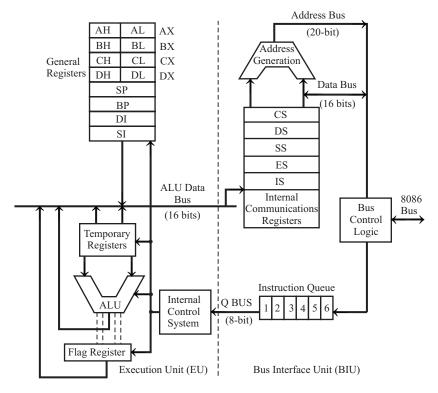

The 8086 has a pipelined architecture. In pipelined architecture the processor will have a number of functional units and the execution time of the functional units are overlapped. Each functional unit works independently most of the time. The simplified block diagram of the internal architecture of an 8086 is shown in Fig. 1.9. The architecture of the 8086 can be internally divided into two separate functional units: **Bus Interface Unit** (BIU) and **Execution Unit** (EU).

The BIU fetches instructions, reads data from memory and IO ports and writes data to memory and IO ports. The BIU contains segment registers, an instruction pointer, an instruction queue, an address generation unit and a bus control unit. The EU executes instructions that have already been fetched by the BIU. The BIU and EU function independently.

The instruction queue is a FIFO (First-In-First-Out) group of registers. The size of the queue is 6 bytes. The BIU fetches the instruction code from memory and stores it in queue. The EU fetches the instruction codes from the queue.

The BIU has four 16-bit segment registers: Code Segment (CS) register, Data Segment (DS) register, Stack Segment (SS) register and Extra Segment (ES) register. The 8086 memory space can be divided into segments of 64 kB. The 4-segment registers are used to hold four segment base addresses. Hence 8086 can directly address 4 segments of 64 kB at any time instant  $(4 \times 64 = 256 \text{ kB})$  within 1 MB memory space). This feature of the 8086 allows the system designer to allocate separate areas for storing program codes and data.

Fig. 1.9: Internal architecture of 8086.

The contents of the segment registers are programmable. Hence the processor can access the code and data in any part of the memory by changing the contents of the segment registers. The memory segment can be continuous, partially overlapped, fully overlapped or disjointed.

**Note:** Since segment registers are programmable it is possible to design multitasking and multiuser systems using 8086. The program code and data for each task/user can be stored in separate segments. The program execution can be switched from one task/user to another by changing the contents of the segment registers.

The dedicated address generation unit generates a 20-bit physical address from the segment base and an offset or effective address. The segment base address is logically shifted left four times and added to the offset. [logically shifting left four times is equal to multiplying it by  $16_{10}$ .]

The address for fetching instruction codes is generated by logically shifting the content of the CS to the left four times and then adding it to the content of the IP (Instruction Pointer). The IP holds the offset address of the program codes. The content of the IP gets incremented by two after every bus cycle. [In one bus cycle the processor fetches two bytes of the instruction code.]

The data address is computed by using the content of the DS or ES as the base address and an offset or effective address specified by the instruction. The stack address is computed by using the content of the SS as the base address and the content of the SP (Stack Pointer) as the offset address or effective address.

The bus control logic of the BIU generates all the bus control signals such as read and write signals for memory and IO. The EU consists of the ALU, the flag register and the general purpose registers. The EU decodes and executes the instructions. A decoder in the EU control system translates the instructions.

The EU has a 16-bit ALU to perform arithmetic and logical operations. The EU has eight numbers of 16-bit general purpose registers. They are AX, BX, CX, DX, SP, BP, SI and DI.

Some of the 16-bit registers can also be used as two numbers of 8-bit registers as given below:

AX - can be used as AH and AL

BX - can be used as BH and BL

CX - can be used as CH and CL

DX - can be used as DH and DL

The general purpose registers can be used for data storage when they are not involved in any special functions assigned to them. These registers are named after special functions carried out by each one of them as given in Table 1.10.

Table 1.10: Special Functions of 8086 Registers

| Register | Name of the register | Special function                                                                                              |

|----------|----------------------|---------------------------------------------------------------------------------------------------------------|

| AX       | 16-bit Accumulator   | Stores the 16-bit result of certain arithmetic and logical operations.                                        |

| AL       | 8-bit Accumulator    | Stores the 8-bit result of certain arithmetic and logical operations.                                         |

| BX       | Base Register        | Used to hold the base value in base addressing mode to access memory data                                     |

| CX       | Count Register       | Used to hold the count value in SHIFT, ROTATE and LOOP instructions.                                          |

| DX       | Data Register        | Used to hold data for multiplication and division operations.                                                 |

| SP       | Stack Pointer        | Used to hold the offset address of top of stack memory.                                                       |

| BP       | Base Pointer         | Used to hold the base value in base addressing using stack segment register to access data from stack memory. |

| SI       | Source Index         | Used to hold the index value of source operand (data) for string instructions.                                |

| DI       | Destination Index    | Used to hold the index value of destination operand (data) for string instruction.                            |

# 1.6.6 8086 Flag Register

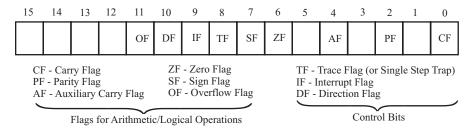

The size of an 8086 flag register is 16 bits and in this nine bits are defined as flags. The six flags are used to indicate the status of the result of the arithmetic or logical operations. Three flags are used to control the processor operation and so they are also called control bits. The various flags of an 8086 processor and their bit position in flag register are shown in Fig. 1.10.

**Fig. 1.10:** Bit positions of various flags in the flag register of 8086.

The Carry Flag (CF) is set if there is a carry from the addition or borrow from the subtraction. Auxiliary carry Flag (AF) is set if there is a carry from low nibble to high nibble of the low order 8-bit of a 16-bit number.

The Overflow Flag (OF) is set to **one** if there is an arithmetic overflow, that is, if the size of the result exceeds the capacity of the destination location. Sign Flag (SF) is set to **one** if the most significant bit of the result is **one** and SF is cleared to **zero** for non-negative result. The **Parity** Flag (PF) is set to **one** if the result has even parity and PF is cleared to **zero** for odd parity of the result. The **Z**ero Flag (ZF) is set to **one** if the result is zero and ZF is cleared to **zero** for a non zero result.

The three control bits in the flag register can be set or reset by the programmer. The **D**irection Flag (DF) is set to **one** for autodecrement and reset to **zero** for autoincrement of the SI and DI registers during string data accessing. Setting Interrupt Flag (IF) to **one** causes the 8086 to recognize the external maskable interrupts, and clearing IF to **zero** disables the interrupts.

Setting Trace Flag (TF) to **one**, places the 8086 in the single step mode. In this mode the 8086 generates an internal interrupt after execution of each instruction. The single stepping is used for debugging a program.

#### 1.6.7 Instruction and Data Flow in 8086

The 8086 microprocessor allows the user to define different memory areas for storing the program and data. The program memory can be accessed using CS-register and the data memory can be accessed using DS, ES and SS registers.

The program instructions are stored in the program memory which is an external device. To execute a program in 8086, the base address and offset address of the first instruction of the program should be loaded in CS-register and IP respectively. The 8086 computes the 20-bit physical address of the program instruction by multiplying the content of the CS-register by  $16_{10}$  and adding to the content of the IP. The 20-bit physical address is given out on the address bus. Then  $\overline{\text{RD}}$  is asserted **low**. Also other control signals necessary for program memory read operation are asserted. The IP is incremented by two to point the next instruction or the next word of the same instruction.

The address and control signals enable the memory to output one word (two bytes) of program memory on the data bus. After a predefined time the  $\overline{RD}$  is asserted **high** and at this instant the content of the data bus is latched into two empty locations of the instruction queue. Then the BIU starts fetching the next word, of the program code as explained above. The BIU keeps on fetching the program codes, word by word, from consecutive memory locations whenever two locations of queue is empty. When a branch instruction is encountered, the queue is emptied and then filled with program codes from the new address loaded in the CS and IP by the branch instruction.

The EU reads the program instructions from the queue, decodes and executes them one by one. If the execution of an instruction requires data from memory (or to store data in memory) then BIU is interrupted to read (or write) data in memory. When BIU is interrupted it completes the fetching of the current instruction word and then starts reading/writing the data by generating a 20-bit data memory address. The 20-bit data memory address is obtained by multiplying the content of the segment base register specified by the instruction by  $16_{10}$  and adding to an effective or offset address specified by the instruction.

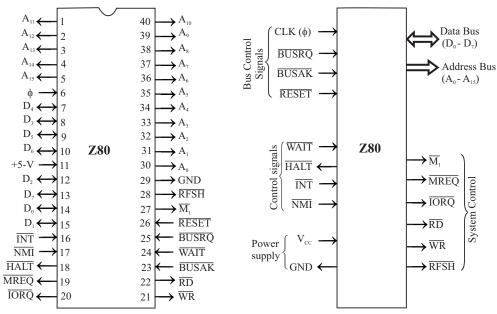

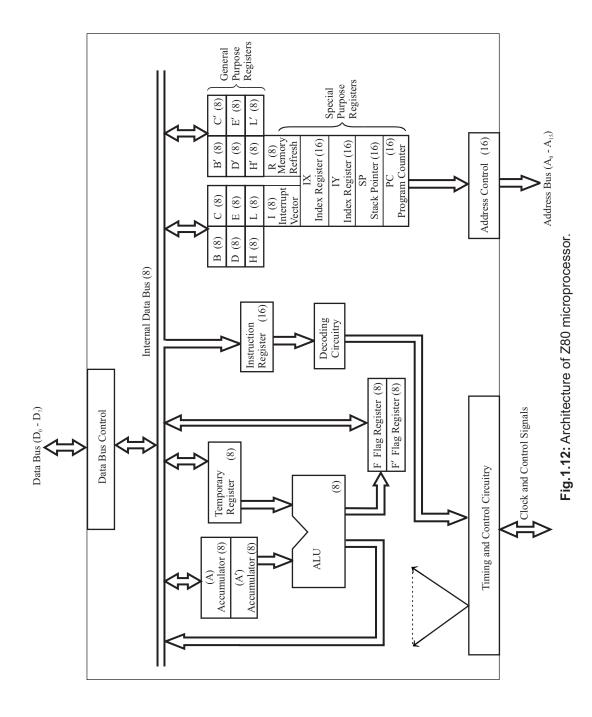

### 1.7 ZILOG Z80

The ZILOG Z80 is an 8-bit microprocessor manufactured using NMOS technology. The Z80 is available in a 40-pin DIP (**D**ual In-line **P**ackage). It requires a single external clock and a single 5-V power supply. The maximum internal clock of standard Z80 is 2.5 MHz and for Z80-A it is 4 MHz. The Z80 provides more registers, extra addressing modes and a much larger instruction set than an 8085. It also has a built-in logic to refresh its dynamic RAM memories.

The signals of Z80 microprocessor and its functional block diagram (architecture) are shown in Figs. 1.11 and 1.12 respectively. The Z80 communicates with other system modules via three functionally separate buses: data, address and control buses.

The Z80 has separate pins for data and address. It operates on an 8-bit data and uses a 16-bit memory address. The physical memory size of the Z80 system is 64 kb. The IO devices can be mapped by memory-mapping or IO-mapping similar to that of 8085. For IO-mapped devices an 8-bit address is allotted. During memory refresh time, the seven lower-order bits of the address bus  $(A_0 - A_6)$  contain a valid refresh address.

Fig. 1.11: Signals of Z80.

The control bus has three types of control signals. They are listed below:

# 1. System control signals

M<sub>1</sub> · First machine cycle of an instruction

MREQ - Memory request

IORQ - IO request

RD - Read control

WR - Write control

RFSH - Refresh cycle

# 2. CPU control signals

WAIT - Wait request

HALT - Halt request

INT - Interrupt request

NMI - Non-maskable interrupt

# 3. Bus control signals

BUSRQ

BUS request

BUSAK

BUS acknowledge

RESET

System reset

CLK (φ)

Clock input

The ALU is eight bits wide and performs similar functions to those of the 8085 ALU. The Z80 has two independent 8-bit accumulators A and A' and two independent flag registers F and F'. The ALU operation involving accumulator A affects the flag register F. The ALU operation involving accumulator A' affects the flag register F'.

The flag registers have six flags: sign (S and S'), zero (Z and Z'), carry (C and C'), parity/over flow (P/V and P'/V'), half carry (H and H') and subtract (N and N').

The Z80 has two sets of 8-bit general purpose register. Each set has 6 registers. They are B, C, D, E, H & L and B', C', D', E', H', & L'. They can be used individually as 8-bit registers or as 16-bit register pairs. The allowed pairs are BC, DE & HL and B'C', D'E' & H'L'.

At any time instant the programmer can select and work with either the main register set or the alternate register set. To work in an alternate register set, the programmer has to use a single Exchange Instruction (EXI) for the entire set of instructions. This alternate set allows the background mode of operation or handling fast interrupt response requirements while servicing an interrupt or executing a subroutine. While executing a program if one set of registers is not sufficient then we need not push them to stack, alternatively we can deactivate them without destroying its contents and switch to an alternate set of registers through exchange instructions.

The 16-bit Program Counter (PC) and Stack Pointer (SP) registers are same as that of a 8085 microprocessor and operate in exactly the same way. The registers IX and IY allow two independent indexed addressing modes.

The Z80 includes an 8-bit interrupt vector (I). It is used in one of the interrupt response modes of the processor. It holds the upper eight bits of a memory pointer (or vector address). The lower eight bits of this pointer are supplied (as a vector number) by the interrupting device that requests service. The CPU then uses this 16-bit vector address to make an indirect call to the memory location that holds the first instruction of the interrupt service routine. This feature allows the vector table to be located anywhere in the memory.

The Z80 also contains an 8-bit memory refresh register (R) that contains the current memory refresh address, thus providing for automatic, totally transparent refresh of external dynamic RAM memories. Although the programmer can load this register for testing purposes, the R register is not normally used by the programmer.

The Z80 can execute 158 instruction types. The microprocessor includes all the instructions of an 8080A microprocessor with total software compatibility at the machine code level.

Note: The 8085 has same instructions of 8080 except two new instructions SIM and RIM. Hence 8085 is also software compatible with Z80.

The new instructions in Z80 include 1/4/8/16-bit operations, exchange instructions, block-transfer and block-search instructions and a full set of rotate and shift instructions applicable to any register, rather than just to the accumulator.

The size of a Z80 instruction is one to four bytes. A 1-byte instruction has just one-byte opcode. A 2-byte instruction has one or two byte opcode plus data-byte/device-number/displacement.

In multibyte instructions the opcode is one or two bytes. The remaining bytes are data/device-number/displacement/address.

The device-number is an 8-bit IO port address. The data-byte is the immediate operand. The displacement is a signed 2's complement number which is added to a 16-bit number residing in an index register, during indexed addressing.

Every Z80 instruction consists of one to six machine cycles. All types of machine cycles consist of either three or four states. Some Z80 instructions always insert wait states ( $T_w$ ) between the states  $T_2$  and  $T_3$ . The basic operation of the Z80 is analogous to that of the INTEL 8085. The main difference is that instead of  $IO/\overline{M}$  of 8085, the Z80 has  $\overline{MREQ}$  and  $\overline{IORQ}$ . They are activated along with  $\overline{RD}$  and  $\overline{WR}$  for the memory or IO access.

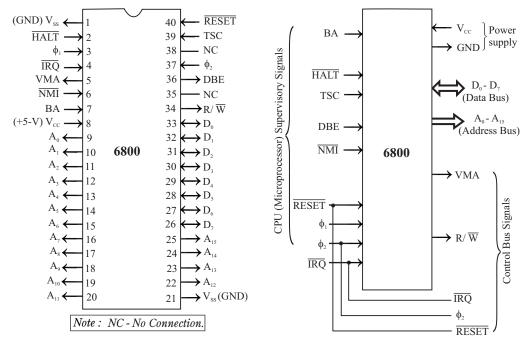

# 1.8 MOTOROLA 6800

The Motorola 6800 product family was originally introduced in 1974. The 6800 microprocessor CPU is manufactured in NMOS technology on a 40-pin chip, has TTL compatible pins and it is the first 8-bit single chip microprocessor to exploit a single 5-V power supply. The 6800 CPU can drive from seven to ten 6800 family devices without buffering. A two-phase external clock (1 MHz, maximum) must be externally supplied.

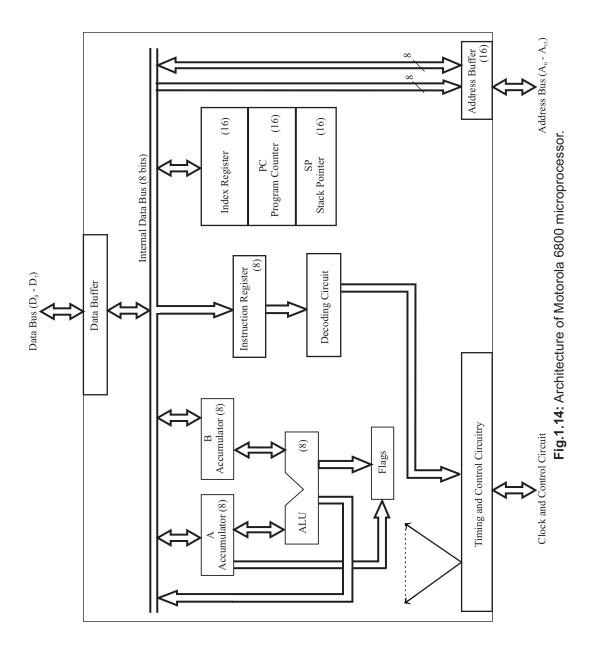

The signals of a motorola 6800 and its simplified functional block diagram are shown in Figs. 1.13 and 1.14 respectively.

The 6800 CPU has three buses to communicate with the other system modules, they are data, address and control buses. The data bus is bidirectional and has 8-lines,  $D_0$ - $D_7$ . The address bus has 16-lines,  $A_0$ - $A_{15}$ . The processor operates on 8-bit data and uses a 16-bit address for memory and IO devices.

Fig.1.13: Signals of Motorola 6800.

This microprocessor does not distinguish between memory and peripheral addresses. Therefore some of the 64k addresses must be reserved for peripheral addresses. The control bus carries two types of signals called **control bus signals** and **CPU** (microprocessor) supervisory signals.

| Control bus signals :     | VMA        | - | Valid memory address   |

|---------------------------|------------|---|------------------------|

|                           | R/W        | - | Read/Write control     |

|                           | IRQ        | - | Interrupt request      |

|                           | $\phi_{2}$ | - | Phase-2 of clock       |

|                           | RESET      | - | System reset           |

| CPU supervisory signals : | BA         |   | Bus acknowledge        |

|                           | HALT       | - | Halt request           |

|                           | TSC        | - | Tristate control       |

|                           | DBE        | - | Data bus enable        |

|                           | NMI        | - | Non-maskable interrupt |

|                           | $\phi_1$   | - | Phase-1 of clock       |

|                           | IRQ        | - | Interrupt request      |

|                           | RESET      | - | System reset           |

The  $\overline{HALT}$  pin is used for DMA data transfer in block-transfer mode or a cycle-stealing mode. When  $\overline{HALT}$  is asserted **low** the microprocessor halts all its activity at the completion of the current instruction.

The Tristate Control (TSC) may be used to implement DMA on a cycle-stealing basis. If TSC is placed in a **high** state, the address bus and the  $R/\overline{W}$  line go to a **high impedance** state 500 ns later. The data bus is not affected by TSC and has its own enable (DBE). This approach assures rapid response to the DMA request. Since the internal memory of the 6800 is dynamic, the TSC terminal cannot be held in **high** state for longer than 5  $\mu$ s, if loss of data in the microprocessor is to be avoided.

The architecture of 6800 includes the ALU, a 16-bit Program Counter (PC), a 16-bit stack pointer, a 16-bit index or general purpose register, a two 8-bit accumulators and a condition code register.

The stack pointer allows a Last-In-First-Out (LIFO) stack to be implemented at any address in the memory and to be limited in size only by the memory space. The index register may be used to store data or a 16-bit memory address for use in the indexed mode of addressing. The Condition Code Register (CCR) indicates the results of an ALU operation. The flags in the CCR are Negative (N), Zero(Z), Overflow (O), Carry(C), Half carry (H) and Interrupt enable/disable (I). The unused bits of the CCR are the 1's.

The ALU performs arithmetic and logical operations including AND, OR, EXCLUSIVE-OR, NEGATE, COMPARE, ADD, SUBTRACT and DECIMAL ADJUST which allows BCD arithmetic to be performed. Immediate, direct, indexed and relative addressing modes are used in 6800.

In the indexed addressing mode, the address contained in the second byte of the instruction is added to the lowest eight bits of the index register. The carry is then added to the higher order bits of the index register. The result is used to address memory.

In relative addressing the address contained in the second byte of the instruction is added to the lowest eight bits of the PC. To this result, a value of  $\pm 2$  is added, which allows the user to address the data within a range of  $\pm 125$  to  $\pm 129$  bytes of the present instruction.

The 6800 has a set of 72 instructions. They are classified as data handling, arithmetic, logic, control transfer, data test, condition codes, address maintenance and interrupt handling.

The data handling instructions include several instructions for moving data between two accumulators, memory and the stack. Data may be altered with Clear, Increment, Decrement, Complement (1's and 2's), Rotate and Shift instructions.

The arithmetic instructions include Add, Subtract and Decimal Adjust Accumulator. The AND, OR and EXCLUSIVE-OR comprise the logical instructions.

The control transfer instructions include Unconditional Branch, Jump and Jump-to-subroutine. The Branch instruction uses relative addressing while the Jump instruction uses direct or indirect addressing. A number of conditional branches are available which test the condition of one or more bits of the condition code register.

The data test instructions set the condition codes (alter the flags) without altering the data. They include Bit Test (for comparing individual bits of accumulator A or B with a memory word), Compare and Test (for determining the sign of a number).

Condition code instructions are provided which enable the programmer to set or reset directly the Carry, Interrupt or Over flow flags. The entire contents of the condition code register may be moved to or from the accumulator A with a single instruction. Eleven instructions are provided for address maintenance. These instructions allow operations on the index register, e.g., Compare, Increment, Decrement and Transfer to or from the memory or the stack pointer. Similar instructions are available for operation on addresses stored in the stack pointer.

The interrupt handling instructions include a **software interrupt** (SWI) which stores the status of the processor in the stack before processing the interrupt and a **Ret**urn from Interrupt (RTI) instruction which restores the status of the microprocessor after an interrupt is processed. A **Wa**it for Interrupt (WAI) instruction causes the status to be stored in the stack and places the processor in a halt condition until a hardware interrupt occurs.

A 6800 instruction may be one, two or three bytes long, its length being closely related to the addressing mode used.

Usually every 6800 instruction cycle consists of two to eight machine cycles, all of which are identical in length (except interrupt instructions which require longer instruction execution cycles.) In the 6800, a machine cycle is one and the same thing as a clock cycle (or state.)

The operation of the 6800 is very simple, since it consists of only three types of machine cycles: a read machine cycle (during which a byte of data is input into the CPU), a write machine cycle (during which a byte of data is output by the CPU) and an interrupt operation machine cycle (during which the CPU is busy and no activity occurs on the system buses.) The timing of any 6800 instruction is simply a concatenation of these three basic machine cycle types.

The control signals required to access a memory location are R/ $\overline{W}$ , VMA and DBE. Under normal circumstances, DBE is identical to  $\phi_2$ . The signal R/W controls the reading or writing operation. For read operation R/ $\overline{W}$  is asserted **low**.

#### 1.9 SUMMARY

- A microprocessor is a program controlled semiconductor device (IC) which fetches, decodes and executes instructions.

- The basic units or blocks of a microprocessor are ALU, an array of registers and a control unit.

- A bus is a group of conducting lines that carries data, address and control signals.

- With n-bit binary we can generate 2" different binary codes or address.

- The three logic levels of tristate logic are high, low and high impedance state.

- The world's first microprocessor INTEL 4004, was released by INTEL corporation in the year 1971.

- The NMOS process offers faster speed and higher density than PMOS and it is TTL compatible.

- The computing system designed using a microprocessor as its CPU is called a microcomputer.

- The EPROM memory is used to store permanent programs and data. RAM is used to store temporary programs and data.

- The computers are classified into Micro, Mini and Large computers.